The MC6809E is a high-performance 8-bit microprocessor which supports modern programming techniques such as position independence, re-entrancy, and modular programming.

This third-generation addition to the M6800 family has major architectural improvements, which include additional registers, instructions, and addressing modes.

The basic instructions of any computer are greatly enhanced by the presence of powerful addressing modes. The MC6809E has the most complete set of addressing modes available on any 8-bit microprocessor.

The MC6809E has hardware and software features which make it an ideal processor for higher level language execution or standard controller applications. External clock inputs are provided to allow synchronisation with peripherals, systems, or other MPUs.

This document contains information on a new product. Specifications and information herein are subject to change without notice.

Symbol Value Unit Supply Voltage VCC -0.3 to +7.0 V Input Voltage Vin -0.3 to +7.0 V Operating Temperature Range

MC6809E, MC68A09E, MC68B09E

MC6809EC, MC68A09EC, MC68B09ECTA TL to TH

0 to +70

-40 to +85°C Storage Temperature Range Tstg -56 to + 150 °C

This device contains circuitry to protect the inputs against damage due to static voltage or electric fields; however, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (e g., either VSS or VCC).

Thermal Resistance Symbol Value Unit Cerdip HJA 60 CW Plastic 100

The average chip-junction temperature, TJ, in °C can be obtained from:

TJ = TA + (PD x ØJA ) (1)

where:

TA = Ambient Temperature, °C

ØJA = Package Thermal Resistance, Junction-to-Ambient, °C W

PD = PINT+ PPORT

PINT = ICC x VCC, Watts - Chip Internal Power

PPORT = Port Power Dissipation, Watts - User Determined

For most applications PPORT < PINT and can be neglected. PPORT may become significant if the device is configured to drive Darlington bases or sink LED loads. An approximate relationship between PD and TJ (if PPORT is neglected) is:

PD = K ÷ (TJ + 273 °C) (2)

Solving equations (1) and (2) for K gives:

K = PD x (TA + 273 °C) + ØJA x PD2 (3)

(VCC 5.0 V ± 5%, VSS = 0 V DC. TA = TL to TH unless otherwise noted).

| CHARACTERISTIC | Symbol | Min | Typ | Max | Unit | |

| Input High Voltage | Logic, Q | VIH | VSS + 2.0 | - | VCC | V |

| !RESET | VIHR | VSS + 4.0 | - | VCC | ||

| E | VIHC | VSS - 0.75 | - | VCC+0.3 | ||

| Input Low Voltage | Logic, !RESET | VIL | VSS - 0.3 | - | VSS - 0.8 | V V V |

| E | VILC | VSS - 0.3 | - | VSS - 0.4 | ||

| Q | VILQ | VSS - 0.3 | - | VSS - 0.6 | ||

| Input Leakage Current (VIN = 0 to 5.25V, VCC - max) |

Logic, Q, !RESET | IIN | - | - | 2.5 | µA |

| E | - | - | 100 | |||

| DC output high voltage | D0-7 | VOH | VSS + 2.4 | - | - | V |

| A0-15, R/!W | VSS + 2.4 | - | - | |||

| BA, BS, LIC, AVMA, BUSY | VSS + 2.4 | - | - | |||

| DC output low voltage (ILOAD = 2.0 mA, VCC = min) | VOL | - | - | VSS + 0.4 | V | |

| Internal Power Dissipation (measured at TA = 0 °C in steady state operation) |

PINT | 1.0 | W | |||

| Capacitance (VIN = 0V, TA = 25°C, f = 1.0 MHz) Measured rather than 100% tested. |

D0-7, Logic, Q, !RESET | CIN | - | 10 | 15 | pf |

| E | - | 30 | 50 | |||

| A0-15, R/!W, BA, BS, LIC, AVMA, BUSY | COUT | - | 10 | 15 | ||

| Frequency of Operation (E and Q inputs) |

MC6809E | f | 0.1 | - | 1.0 | MHz |

| MC68A09E | 0.1 | - | 1.5 | |||

| MC68B09E | 0.1 | - | 2.0 | |||

| Hi-Z (off-state) input current, (VIN = 0.4 to 2.4V, VCC - max) |

D0-7 | ITSI | - | 2.0 | 10 | µA |

| A0-15, R/!W | - | - | 100 | |||

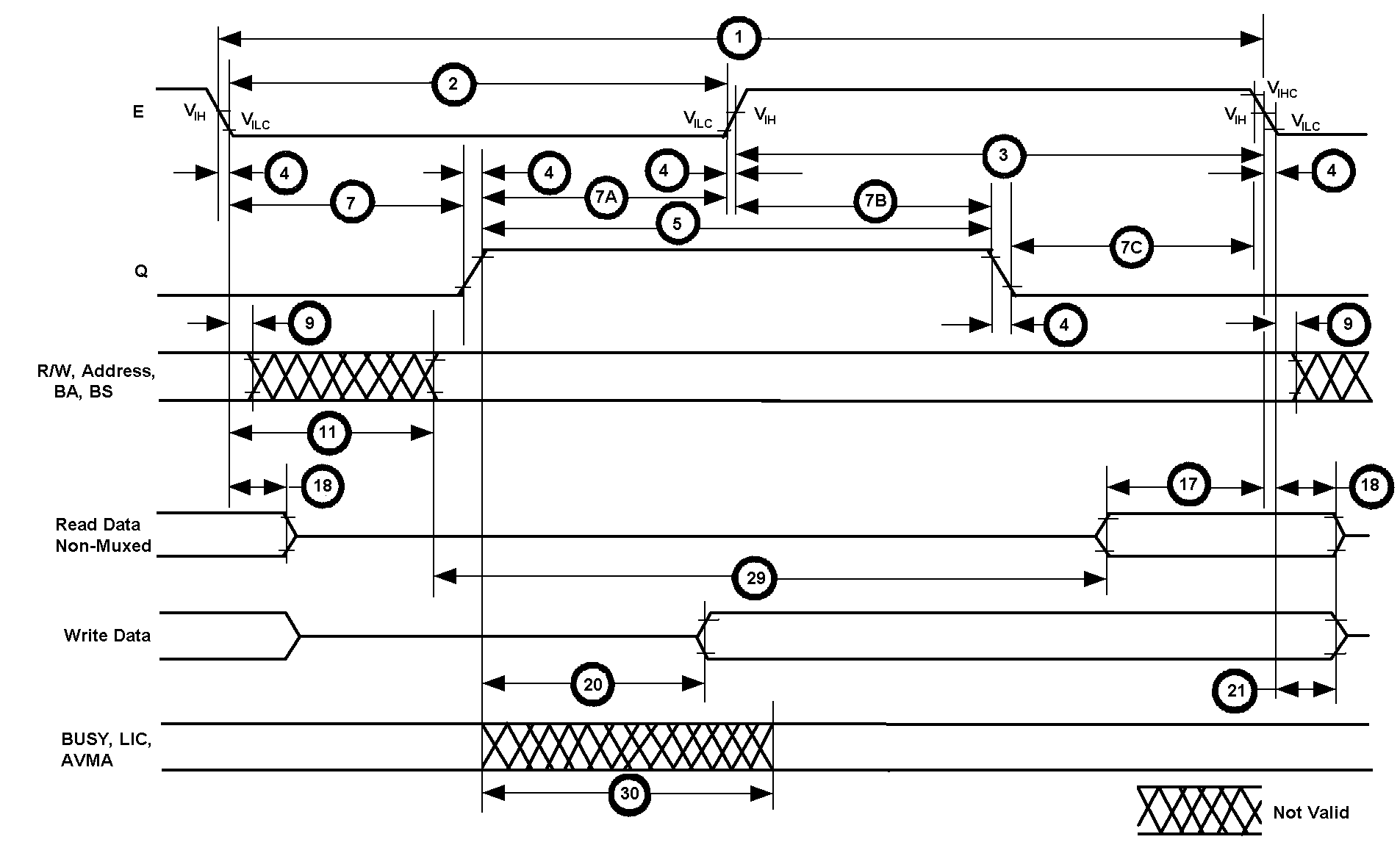

| Ident. Number |

Characteristics | Symbol | MC6809E | MC68A09E | MC68B09E | Unit | |||

| Min. | Max. | Min. | Max. | Min. | Max. | ||||

| 1 | Cycle Time | TCYC | 1.0 | 10 | 0.667 | 10 | 0.5 | 10 | µs |

| 2 | Pulse Width, E Low | PWQH | 450 | 9500 | 295 | 9500 | 210 | 9500 | ns |

| 3 | Pulse Width, E High | PWEH | 450 | 9500 | 280 | 9500 | 220 | 9500 | ns |

| 4 | Clock rise and fall time | tr, tf | - | 25 | - | 25 | - | 25 | ns |

| 5 | Pulse Width, Q High | PWQH | 450 | 9500 | 280 | 9500 | 220 | 9500 | ns |

| 7 | Delay Time, E to Q Rise | tEQ1 | 200 | - | 130 | - | 100 | - | ns |

| 7A | Delay Time, Q High to E Rise | tEQ2 | 200 | - | 130 | - | 100 | - | ns |

| 7B | Delay Time, E High to Q Fall | tEQ3 | 200 | - | 130 | - | 100 | - | ns |

| 7C | Delay Time, Q High to E Fall | tEQ4 | 200 | - | 130 | - | 100 | - | ns |

| 9 | Address Hold Time | tAH | 20 | - | 20 | 20 | - | ns | |

| 11 | Address Delay Time from E Low (BA, BS, R/!W) | tDH | - | 200 | - | 140 | - | 110 | ns |

| 17 | Read Data Setup Time | tDSR | 80 | - | 60 | - | 40 | - | ns |

| 18 | Read Data Hold Time | tDHR | 10 | - | 10 | - | 10 | - | ns |

| 20 | Data Delay Time from Q | tDDQ | - | 200 | - | 140 | - | 110 | ns |

| 21 | Write Data Hold Time | tDHW | 30 | - | 30 | - | 30 | - | ns |

| 29 | Usable Access Tirne | tACC | 695 | - | 440 | - | 330 | - | ns |

| 30 | Control Delay Time | tCD | - | 300 | - | 250 | - | 200 | ns |

| - | Interrupts, !HALT, !RESET and TSC Setup Time (Figures 6, 7, 8, 9, 12 and 13) |

tPCS | 200 | - | 140 | - | 110 | - | ns |

| - | TSC Dnve to Valid Logic Level | tTSV | - | 210 | - | 150 | - | 120 | ns |

| - | TSC Release MOS Buffers to High Impedance (Figure 13) | tTSR | - | 200 | - | 140 | - | 110 | ns |

| - | TSC Hi-Z Delay Time (Figure 13) | tTSD | - | 120 | - | 85 | - | 80 | ns |

| - | Processor Control Rise and Fall Time (Figure 7) | tPCS tPCS |

- | 100 | - | 100 | - | 100 | ns |

FIGURE 1 - READ/WRITE DATA TO MEMORY OR PERIPHERALS TIMING DIAGRAM

NOTES.

FIGURE 2 - EXPANDED BLOCK DIAGRAM

| -> | Buffers * | --> | A0-15 | ||||||

| <-> | Buffers * | <-> | D0-7 | ||||||

| v | |||||||||

| <-> | PC | <-> | Instruction register |

||||||

| <-- | U | <-> | |||||||

| <-> | S | <-> | v | ||||||

| <-- | Y | <-> | Interrupt Control |

<-- | !RESET | ||||

| <-- | X | <-> | <-- | !NMI | |||||

| <-- | D{ | A | <-> | <-- | !FIRQ | ||||

| B | <-> | <-- | !IRQ | ||||||

| <-- | DP | CC | <-> | ^ v | |||||

| v | Bus Control |

--> | LIC | ||||||

| ALU | <-> | --> | AVMA | ||||||

| * Buffers are tristated by TSC |

--> | R/!W | |||||||

| <-- | TSC | ||||||||

| <-- | HALT | ||||||||

| --> | BA | ||||||||

| ^ v | |||||||||

| Timing | <-- | E | |||||||

| <-- | Q | ||||||||

FIGURE 3 - BUS TIMING TEST LOADC = 30 pf for BA, BS, LIC, AVMA, BUSY

130 pF for D0-7

90 pF for A0-15, R/!W

R = 11.7 k for D0-7

18.5 k for A0-15. R/!W

24 k for BA, BS, LIC, AVMA, BUSY

|

| Package type | Frequency | Temperature range | Order number |

Plastic P Suffix |

1.0 MHz 1.0 MHz 1.5 MHz 1.5 MHz 2.0 MHz 2.0 MHz |

0ºC to 70ºC -40ºC to 85ºC 0ºC to 70ºC -40ºC to 85ºC 0ºC to 70ºC -40ºC to 85ºC |

MC6809EP MC6809ECP MC68A09EP MC68A09ECP MC68B09EP MC68B09ECP |

Cerdip S Suffix |

1.0 MHz 1.0 MHz 1.5 MHz 1.5 MHz 2.0 MHz 2.0 MHz |

0ºC to 70ºC -40ºC to 85ºC 0ºC to 70ºC -40ºC to 85ºC 0ºC to 70ºC -40ºC to 85ºC |

MC6809ES MC6809ECS MC68A09ES MC68A09ECS MC68B09ES MC68B09ECS |